# PROJETO E SIMULAÇÃO DE CIRCUITOS INTEGRADOS CMOS PARA ESPECTROSCOPIA DE BIOIMPEDÂNCIA ELÉTRICA

<sup>1</sup>PABLO DUTRA DA SILVA, <sup>2</sup>PEDRO BERTEMES FILHO

<sup>1</sup>Instituto Federal de Santa Catarina (IFSC),

<sup>2</sup>Universidade do Estado de Santa Catarina (UDESC)

<pablo.silva@ifsc.edu.br>, <pedro.bertemes@udesc.br>

DOI: 10.21439/conexoes.v19.3469

**Resumo.** Este trabalho faz parte do projeto EGluco do grupo PETBIO da Universidade do Estado de Santa Catarina. O objetivo é desenvolver um dispositivo vestível que faça a medição, principalmente, de glicemia de forma não invasiva utilizando diferentes tipos de sensores. Com base na literatura sobre dispositivos vestíveis e nos resultados do protótipo atual do projeto EGluco, percebe-se que a tecnologia de circuitos integrados é a mais indicada para um efetiva miniaturização e redução de consumo de energia. Neste contexto, é proposto neste trabalho uma análise de viabilidade do uso de um simulador de distribuição gratuita que apresente, além do simulador *SPICE*, uma ferramenta de captura de esquemático e uma ferramenta de apresentação de resultados gráficos. Foi desenvolvido um macromodelo *SPICE* dos transistores da tecnologia de fabricação 0,18  $\mu\text{m}$  para o simulador de distribuição gratuita *TINA-TI*. O modelo foi testado realizando testes de extração de parâmetros para o modelo ACM do transistor MOSFET, tanto para os amplificadores fonte comum como para o amplificador de transcondutância. O macromodelo e o simulador indicaram resultados confiáveis com erro máximo de aproximadamente 11% nos valores simulados em comparação com a especificação do circuito arbitrada para os amplificadores fonte comum. Já para o amplificador de transcondutância o erro máximo apresentado foi de aproximadamente 16%, para o caso do *slew rate*. Apesar destas discrepâncias em relação as especificações originais, o OTA apresenta desempenho compatível com a aplicação a que se pretende.

**Palavras-chave:** circuitos integrados CMOS; amplificador OTA; dispositivo vestível; espectroscopia de bioimpedância elétrica.

## CMOS INTEGRATED CIRCUIT DESIGN AND SIMULATION FOR ELECTRICAL BIOIMPEDANCE SPECTROSCOPY

**Abstract.** The aim of the EGluco Project, developed in the PETBIO group at the State University of Santa Catarina, is to develop a wearable device, with multiple sensors, to measure glucose in a noninvasive way. An analysis of the literature about wearables for glucose measurement, their use in health care, and the actual stage of development of EGluco hardware concluded that using integrated circuit design is imperative to achieve miniaturization and power consumption of a typical wearable. To initiate explorations in CMOS circuit design, for the EGluco project, a viability analysis of the use of a free distribution SPICE simulator which comprehends schematic capture, SPICE simulator, and results viewer was proposed for this work. For this analysis, two SPICE transistors macro models of the 0,18  $\mu\text{m}$  fabrication technology were developed for a free distribution simulator (*TINA-TI*). These macro models were tested through extraction by simulation of technological physical parameters for the analytical MOSFET model Advanced Compact Model (ACM). After that, the macro models were used in common-source amplifiers design using ACM. And finally, a differential transconductance amplifier that will be applied in a current source for impedance spectroscopy analysis hardware. Both the simulator and the macro model were reliable presenting a maximum error of 11% for the performance parameters of the common source amplifier compared with the specifications set for design. In the case of the transconductance amplifier, the maximum error of the performance parameter concerning the specifications was 16% for the slew rate. Despite some errors in relation to the original specifications, the OTA presents compatible performance with the target application.

**Keywords:** CMOS integrated circuit; operational transconductance amplifier (OTA); wearable device; electrical bioimpedance spectroscopy.

## 1 INTRODUÇÃO

Dispositivos vestíveis como por exemplo, relógios, pulseiras, faixas peitorais, tênis, dentre outros estão cada vez mais difundidos comercialmente para o monitoramento de dados relacionados ao estilo de vida das pessoas. Além de número de passos, distâncias percorridas, velocidade há também os parâmetros médicos como saturação de oxigênio no sangue e batimentos cardíacos (Miao *et al.*, 2023; Mizuno; Changolkar; Patel, 2021; Vijayan *et al.*, 2021). É importante lembrar que, para um parâmetro ser oferecido ao consumidor em um dispositivo vestível este deve ser coletado de forma não invasiva, pois do contrário, seria desconfortável e o consumidor deixaria de utilizá-lo facilmente. Outro requisito é que deve ser compacto e agradável esteticamente para que possa ser utilizado nos mais diversos ambientes sem constrangimentos. E finalmente, como é alimentado com baterias, deve ser de baixo consumo de energia.

Todos os requisitos anteriormente citados tornam os dispositivos vestíveis obrigatoriamente altamente integrados e por isso usam as tecnologias VLSI (*Very Large Scale of Integration*) para construir tais dispositivos com várias funções em volumes muito pequenos. Pode-se resumir a sigla VLSI como circuitos integrados, portanto, não é possível realizar um vestível sem a aplicação direta de circuitos integrados e o desenvolvimento de um ASIC (*Application Specific Integrated Circuit*) onde se desenvolve um circuito integrado específico para as necessidades de um determinado produto como por exemplo os espectrômetros de bioimpedância elétrica apresentados em (Corbacho *et al.*, 2022; Valente; Demosthenous, 2016).

No contexto do projeto EGluco, onde pretende-se desenvolver um dispositivo vestível para a medição de glicemia na forma de um relógio inteligente, faz todo o sentido iniciar o mais rápido possível um aprofundado estudo e projeto de um circuito integrado que abarque suas funcionalidades. Atualmente o dispositivo está montado com circuitos integrados de uso geral de forma discreta, o que o torna volumoso e de alto consumo de energia.

O objetivo deste trabalho é de iniciar os estudos e explorações do projeto de circuitos integrados CMOS por meios de simulação utilizando um simulador de distribuição gratuita ou um *open source*. Para isso é necessário: obter um *software* que tenha a implementação de modelos *SPICE* dos transistor MOSFET integrado, desenvolver um macromodelo para o transistor MOSFET integrado para uma determinada tecnologia de fabricação, realizar os testes de confiabilidade deste macromodelo e da implementação do modelo do transistor no simulador, iniciar os estudos de modelos analíticos com projetos simples de amplificador, iniciar projetos mais complexos como o de um amplificador de transcondutância (OTA - sigla em Inglês) e aplicar o projeto do OTA a uma fonte de corrente controlada por tensão para espectroscopia de bioimpedância elétrica. Todos os resultados dessas etapas são discutidos neste trabalho nas seções seguintes.

## 2 FUNDAMENTAÇÃO E EQUACIONAMENTO TEÓRICOS

Nesta seção pretende-se apresentar as equações do modelo do transistor MOSFET que será utilizado para fazer os cálculos dos projetos além das equações de circuito dos projetos que foram implementados neste trabalho. O modelo de MOSFET será o *Advanced Compact MOSFET* (ACM) (Adornes *et al.*, 2022) “*Advanced Compact MOSFET*” (Coitinho; Spiller; Schneider, 2000; Machado *et al.*, 2011; Schneider; Galup-Montoro, 2010; Siebel; Galup-Montoro, 2007) e suas equações são utilizadas para fundamentar os procedimentos de verificação do modelo *SPICE* que será utilizado nas simulações dos projetos dos circuitos. O primeiro procedimento de verificação será o de extração de parâmetros do modelo ACM por simulação e a sua comparação com a extração de parâmetros via mapeamento dos parâmetros para o modelo BSIM (*Berkeley Short-channel IGFET Model*) que são disponibilizados pelo fabricante.

A confiabilidade do modelo ACM poderá ser verificada com o projeto de amplificadores fonte comum. Depois disso se fará um projeto de um amplificador operacional de transcondutância e se fará uma proposição de aplicação deste OTA em um conversor tensão-corrente.

### 2.1 Modelo *Advanced Compact MOSFET*

O modelo ACM é um modelo matemático para o transistor MOSFET que é fundamentado na densidade de cargas no canal do transistor. Ele apresenta simetria entre fonte de dreno completamente preservada e o equacionamento respeita a conservação da carga. Diversos trabalhos vêm, no decorrer de anos, provando a veracidade destas características. (Adornes *et al.*, 2022; Machado *et al.*, 2011; Schneider; Galup-Montoro, 2010; Siebel; Galup-

Montoro, 2007). Uma característica importante do modelo é que ele necessita de uma quantidade relativamente pequena de parâmetros tecnológicos para a realização de simulação. Diferentemente do modelo BSIM 3.

O modelo ACM contém equações simplificadas e precisas em todos as regiões de operação para o cálculo manual dos projetos. Este conjunto de equações para projeto de transistores na condição de saturação e aproximação de canal longo são: o nível de inversão direto

$$if = \frac{I_D}{I_S} \quad (1)$$

onde  $I_D$  é a corrente de dreno e  $I_S$  é a corrente específica, que é dada por:

$$I_S = I_{SQ} \frac{W}{L} = \frac{\mu_0 C'_{ox} n \varphi_t^2}{2} \frac{W}{L} \quad (2)$$

onde a  $I_{SQ}$  é a corrente específica por quadrado,  $W$  é a espessura do canal,  $L$  é o comprimento do canal,  $\mu_0$  a mobilidade dos portadores,  $C'_{ox} = \varepsilon_{ox}/T_{OX}$  é a capacidade de porta por quadrado,  $n$  é o fator de rampa e  $\phi_t = kT/q$  é a tensão térmica (onde  $k$  é a constante de Boltzman,  $T$  é a temperatura absoluta e  $q$  a carga do elétron), transcondutância de porta de pequeno sinal

$$gmg = \frac{I_D}{n \varphi_t} \frac{2}{\sqrt{1 + if} + 1} \quad (3)$$

a razão de aspecto inversa

$$\frac{L}{W} = \frac{2\mu_0 C'_{ox} \varphi_t}{gmg} \left( \frac{I_D}{ngmg \varphi_t} - 1 \right) \quad (4)$$

a tensão dreno-fonte de saturação

$$V_{DS(sat)} = \varphi_t (\sqrt{1 + if} + 3) \quad (5)$$

a equação do modelo unificado de controle de cargas (UCCM – em Inglês)

$$V_p - V_s = \varphi_t \left[ \sqrt{1 + if} - 2 + \ln(\sqrt{1 + if} - 1) \right] \quad (6)$$

onde  $V_p$  é a tensão de *pinch-off* e  $V_s$  é a tensão de fonte do transistor. A relação entre a tensão de *pinch-off*, a tensão de porta ( $V_G$ ) e a tensão de limiar ( $V_{T0}$ ) é dada por

$$V_p = \frac{V_G - V_{T0}}{n} \quad (7)$$

Com base nas equações (1) a (7) e nos parâmetros tecnológicos, é possível projetar transistores para qualquer topologia de circuito integrado analógico, desde que operem na região de saturação. Caso os transistores operem na região linear, é necessário utilizar as equações completas. As equações apresentadas são aproximações válidas para transistores de canal longo, definidos como aqueles cujo comprimento de canal é, no mínimo, dez vezes maior que o comprimento mínimo da tecnologia empregada. O modelo ACM inclui equações adicionais que consideram efeitos de segunda ordem em transistores de canal curto, mas estes não foram considerados neste trabalho, dado que, em circuitos analógicos, prefere-se o uso de transistores de canal longo.

Os parâmetros tecnológicos, mencionados anteriormente, para o modelo ACM são os apresentados na Tabela 1, que foi adaptada de Coitinho, Spiller e Schneider (2000). Os parâmetros físicos e tecnológicos aqui apresentados são sempre exigidos pelo simulador que esteja utilizando o modelo ACM, mas para fins de projeto manual se utiliza os parâmetros  $V_{T0}$ ,  $T_{OX}$  e  $\mu_0$ .

Com o objetivo de iniciar os estudos e a prática em projeto de circuitos integrados, utilizou-se o modelo ACM para os projetos analíticos e o simulador TINA-TI, que adota o modelo BSIM 3. Para viabilizar o uso desse simulador gratuito como ferramenta de baixo custo, foram desenvolvidos macromodelos *SPICE* dos transistores NMOS e PMOS. Inicialmente, apenas esses dois componentes foram implementados, com a possibilidade futura de inclusão de resistores e capacitores. A criação dos macromodelos exigiu adaptações na linguagem *SPICE*, o que levou à realização de diversos testes comparativos, incluindo simulações de amplificadores fonte comum e um *benchmark* com o simulador open source *NGSPICE*. Os resultados desses testes são apresentados na Seção 3.

**Tabela 1:** Listagem de parâmetros tecnológicos do modelo ACM.

| Parâmetro          | Descrição                                                                 | Unidade                 |

|--------------------|---------------------------------------------------------------------------|-------------------------|

| TOX                | Espessura do óxido de porta                                               | m                       |

| VTO ( $V_{TO}$ )   | Tensão de limiar ( $V_{DB} = V_{SB} = 0$ )                                | V                       |

| GAMMA ( $\gamma$ ) | Coeficiente de efeito de corpo                                            | $\sqrt{V}$              |

| PHI ( $\phi_0$ )   | Potencial de superfície                                                   | V                       |

| U0 ( $\mu_0$ )     | Mobilidade dos portadores                                                 | $\text{cm}^2/\text{Vs}$ |

| THETA ( $\theta$ ) | Coeficiente de redução de mobilidade devido ao campo elétrico transversal | 1/V                     |

| VMAX               | Velocidade limite dos portadores                                          | m/s                     |

| SIGMA ( $\sigma$ ) | Coeficiente DIBL                                                          | $\text{m}^2$            |

| PCLM               | Coeficiente CLM                                                           | -                       |

| LD                 | Difusão Lateral                                                           | m                       |

| XJ                 | Profundidade das Junções                                                  | m                       |

Fonte: Adaptado de Coitinho, Spiller e Schneider (2000)

## 2.2 Projeto do amplificador fonte comum

De acordo com a literatura clássica de eletrônica, o modelo de pequeno sinal pode ser utilizado para calcular o ganho de amplificadores com transistores. Esse modelo representa o transistor por meio de uma impedância de entrada idealmente infinita entre porta e fonte, e uma fonte de corrente controlada pela tensão VGS entre dreno e fonte — caracterizando uma estrutura do tipo VCCS (fonte de corrente controlada por tensão) (Santos, 2022). O ganho de transcondutância é determinado pela multiplicação dessa fonte pela tensão VGS (Santos, 2022).

Considerando que para um modelo idealizado,  $R_o \rightarrow \infty$ . Então, resistor ligado ao dreno é a carga do amplificador em pequeno sinal. Sendo assim, o ganho de tensão será dado por

$$A_v = \frac{v_o}{v_i} = \frac{v_o}{v_{gs}} = -g_m R_D \quad (8)$$

Assim, com a equação (8), pode-se definir a partir do ganho de tensão especificado tanto a característica do transistor gm quanto o valor de RD. Além disso, pode-se definir a corrente de dreno com a equação (9) aplicando as especificações de tensões de polarização  $v_o(\text{CC})$  e a tensão de alimentação VDD e o RD definido na equação (8). A tensão  $v_o(\text{CC})$  é dada por

$$v_o(\text{CC}) = V_{DD} - I_D \cdot R_D \quad (9)$$

As mesmas equações são válidas para o amplificador fonte comum com transistores PMOS, guardadas as diferenças de polarização CC.

## 2.3 Projeto do amplificador operacional de transcondutância

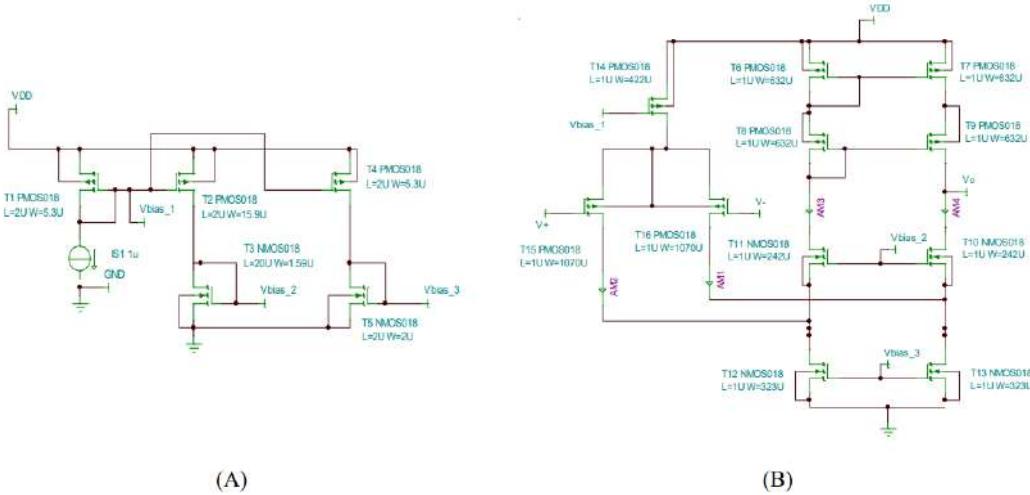

O esquemático do amplificador de transcondutância projetado é apresentado na Figura 1(B). Nele, os transistores T15 e T16 compõem o par diferencial de entrada, enquanto o transistor T14 atua como fonte de corrente de calda. Os demais transistores formam uma carga do tipo *folded cascode*, que proporciona alta impedância de saída. As especificações do projeto foram definidas de forma arbitrária, com o objetivo de realizar um primeiro projeto, adquirir familiaridade com o processo de simulação e desenvolver confiança no método de projeto desse tipo de amplificador, fundamental em circuitos integrados analógicos.

A Figura 1(A) mostra o diagrama esquemático do circuito de polarização do espelho *folded cascode*, responsável por gerar as correntes de polarização tanto para a fonte de corrente quanto para a porção inferior (NMOS) do espelho, enquanto a parte superior (PMOS) é autopolarizada. As especificações adotadas incluem:  $V_{DD} = 3$  V,  $GBW \geq 20$  MHz,  $\text{Slew Rate} \geq 12$  V/ $\mu$ s, capacidade de carga de 10 pF, ganho de malha aberta  $\geq 80$  dB, margem de fase  $\geq 60^\circ$ , e consumo de potência de 2 mW. O projeto do amplificador de transcondutância tem início a partir

## PROJETO E SIMULAÇÃO DE CIRCUITOS INTEGRADOS CMOS PARA ESPECTROSCOPIA DE BIOIMPEDÂNCIA ELÉTRICA

**Figura 1:** Diagrama esquemático (A) do circuito de polarização e (B) do amplificador de transcondutância com espelho *folded cascode*.

de duas especificações principais, ligadas ao dimensionamento dos transistores do par diferencial e do espelho de corrente. Para o par diferencial, define-se a transcondutância ( $g_{mg}$ ) por meio da equação (10), enquanto o *Slew Rate*, descrito pela equação (11), determina a corrente mínima necessária no espelho *cascode* em função da carga capacitiva (Advanced Compact MOSFET, 2023).

Com as especificações de  $GBW$ ,  $SR$  e  $C_L$  pode-se calcular  $g_{mg} \approx 1,88 \text{ mS}$  e  $I_D \approx 240 \mu\text{A}$ . O  $g_{mg}$  será utilizado para definir as correntes para o par diferencial de entrada e a corrente  $I_D$  é a corrente do espelho *cascode*. Para respeitar o consumo de potência máxima especificada pode-se consumir uma corrente total de  $660 \mu\text{A}$ . Para alcançar o  $g_{mg}$  calculado, utilizou-se a equação (3) para calcular a corrente do par diferencial de  $160 \mu\text{A}$ . Já o consumo do circuito de polarização apresentado na Figura 1 ficará arbitrado em  $5 \mu\text{A}$ . A soma de todos estes valores mantém o consumo máximo estipulado mantido. O detalhamento do projeto de cada transistor pode ser verificado na Seção 3.

### 3 EXTRAÇÃO DE PARÂMETROS DO MODELO ACM E PROJETOS DOS 17 AMPLIFICADORES

O simulador TINA-TI foi escolhido para este estudo devido à sua interface intuitiva, flexibilidade no desenvolvimento de macromodelos *SPICE* personalizados e implementação do modelo BSIM 3, amplamente utilizado e bem documentado para diversos processos de fabricação CMOS. Essas características não estão disponíveis em todos os simuladores gratuitos ou *open source* pesquisados. Como não havia necessidade imediata de um projeto físico (*layout*) dos circuitos, optou-se por iniciar os testes com uma ferramenta de baixo custo. O primeiro teste realizado foi a extração de parâmetros do modelo ACM por simulação, que foram então comparados com os parâmetros do modelo BSIM para validação.

#### 3.1 Extração de parâmetros via simulação pelo método da razão de $\frac{g_{mg}}{I_D}$

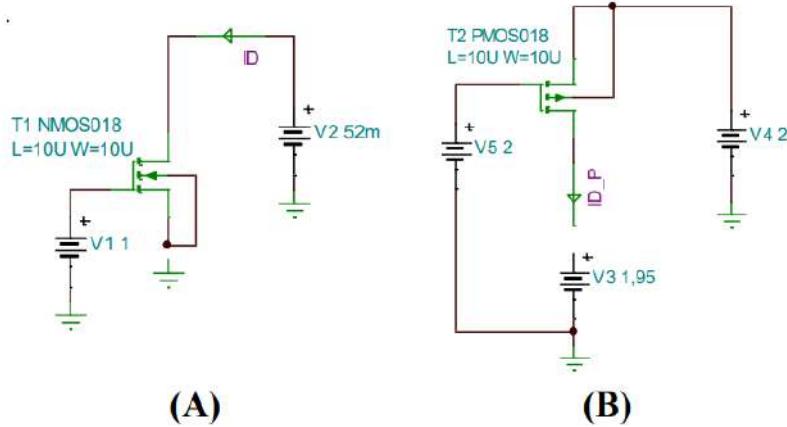

A extração de parâmetros pelo método  $\frac{g_{mg}}{I_D}$  consiste em fazer uma varredura da tensão de porta do transistor enquanto ele é mantido na região linear ( $V_{DS} \ll V_{DS(sat)}$ ), neste caso utilizou-se a tensão  $V_{DS} = 7 \text{ mV}$ , e medir a corrente de dreno. A varredura da tensão de porta foi de  $0 \leq V_{GB} \leq 2 \text{ V}$ . Os diagramas esquemáticos dos testes em questão estão apresentados na Figura 2(A) para o transistor NMOS e na Figura 2(B) para o transistor PMOS.

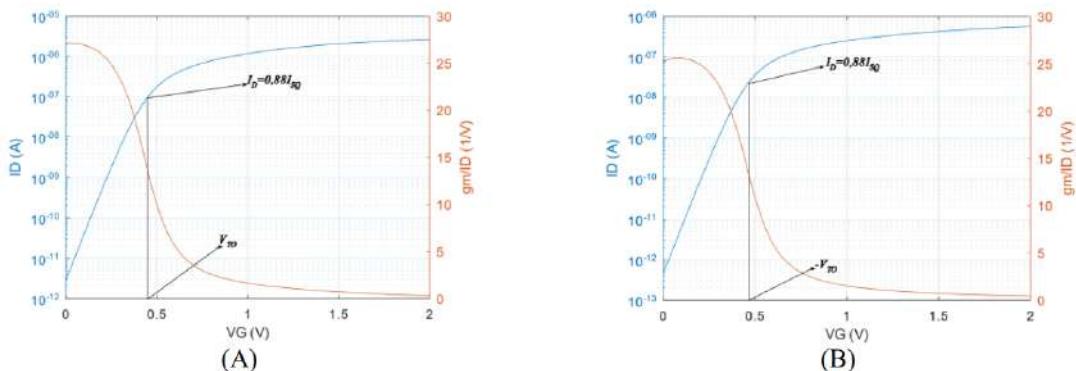

Em seguida faz-se a derivada da corrente de dreno em relação à tensão de porta para se obter  $g_{mg}$  e faz-se o traçado da corrente de dreno e da razão da transcondutância pela corrente no mesmo gráfico, ambos em função da tensão de porta. A Figura 3(A) apresenta os gráficos do teste para o transistor NMOS enquanto a Figura 3(B) apresenta os resultados do teste para o transistor PMOS. Além disso, as figuras citadas apresentam os pontos de definição tanto da tensão de limiar quanto da corrente específica.

Figura 2: Circuitos para Extração de Parâmetros do Transistor (A) NMOS e (B) PMOS.

Para se obter o parâmetro  $V_{T0}$  encontra-se a tensão de porta correspondente a aproximadamente metade do valor máximo encontrado para a razão  $\frac{g_{mg}}{I_D}$ . Para determinar  $I_{SQ}$ , que é independente da razão de aspecto do transistor como pode ser verificado em (2), utiliza-se um transistor quadrado. No teste em questão, escolheu-se arbitrariamente  $W = 10 \mu\text{m}$  e  $L = 10 \mu\text{m}$ .

Com a tensão de limiar, determinada anteriormente, pode-se identificar uma corrente de dreno correspondente a  $I_D \approx 0,88I_{SQ}$ . Por fim, calculou-se  $n$  a partir de (3), sabendo que no ponto em que a razão  $\frac{g_{mg}}{I_D}$  é máxima esta é igual a  $\frac{1}{n\varphi_t}$ . O valor de  $\varphi_t$  utilizado foi de aproximadamente 26 mV, que corresponde a uma temperatura de 27°C. Um resumo dos valores encontrados pode ser verificado na Tabela 2, onde também se verifica um valor mapeado a partir dos parâmetros do modelo BSIM3.

Figura 3: Resultados do método gm/ID para extração de parâmetros do (A) NMOS

Os parâmetros  $I_{SQ}$  foram calculados a partir dos dados de espessura do óxido ( $t_{ox}$ ), mobilidade dos portadores ( $\mu_0$ ) e tensão de limiar ( $V_{T0}$ ), enquanto o fator de rampa foi extraído por simulação. O simulador TINA-TI utiliza o modelo BSIM3 devido à facilidade de acesso aos parâmetros tecnológicos, sendo amplamente implementado nas ferramentas profissionais de projeto de circuitos integrados. Embora seja possível utilizar outros modelos, como o ACM, o BSIM3 oferece uma maior quantidade de ferramentas e informações técnicas.

Os resultados apresentados na Tabela 2 mostram que tanto o modelo do simulador quanto os macromodelos SPICE desenvolvidos são confiáveis. Para garantir a precisão, foram aplicados diversos métodos de extração de  $I_{SQ}$ . Além disso, testes adicionais foram realizados com os macromodelos em projetos simples, incluindo dois amplificadores fonte comum, para verificar sua confiabilidade em projetos mais complexos com múltiplos transistores.

**Tabela 2:** Resumo da extração de parâmetros.

| <b>Origem</b>        | <b>NMOS</b>   |               |          | <b>PMOS</b>   |               |     |

|----------------------|---------------|---------------|----------|---------------|---------------|-----|

|                      | $I_{SQ}$ (nA) | $V_{T0}$ (mV) | $n$      | $I_{SQ}$ (nA) | $V_{T0}$ (mV) | $n$ |

| Simulação            | 85            | 438           | 1,4<br>2 | 31,23         | -462          | 1,5 |

| TINA-TI              |               |               |          |               |               |     |

| Cálculo <sup>a</sup> | 99            | 373           | 1,4<br>2 | 38            | -407          | 1,5 |

<sup>a</sup> Calculados com base nos dados fornecidos pelo fabricante e pelas equações de  $I_S$  do modelo ACM.

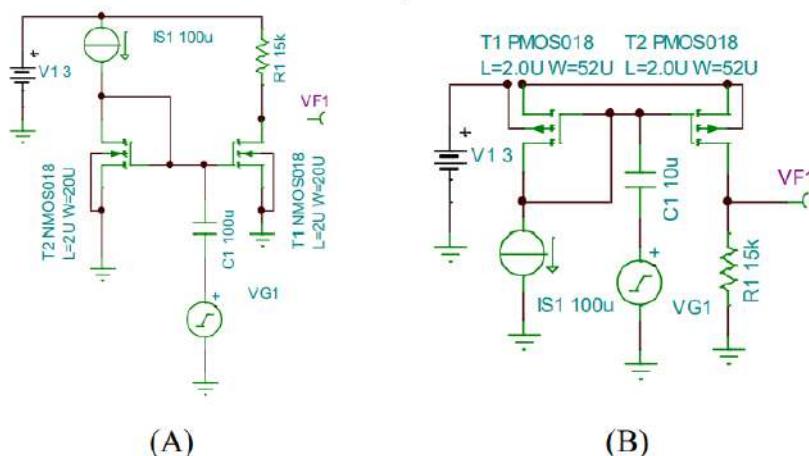

### 3.2 Projeto dos amplificadores fonte comum

O projeto e simulação de dois amplificadores fonte comum foram realizados para testar a confiabilidade dos macromodelos *SPICE* desenvolvidos para o simulador gratuito TINA-TI. Embora os modelos já tivessem sido validados em relação à extração de parâmetros em corrente contínua (CC), foi necessário verificar seu desempenho em simulações transientes e no domínio da frequência. Para isso, escolheu-se o projeto simples do amplificador fonte comum como teste.

**Tabela 3:** Resultados do projeto dos amplificadores fonte comum.

| <i>Projetos para o MOSFET NMOS</i> |          |                |                  |       |            |                 |

|------------------------------------|----------|----------------|------------------|-------|------------|-----------------|

| $g_m$ (S)                          | $i_f$    | $W/L$          | $W(\mu\text{m})$ | $A_v$ | $A_v$ (dB) | $V_{Dsat}$ (mV) |

| 2,64 m                             | 0,1<br>0 | 10032,1<br>0   | 20064,2<br>0     | 39,7  | 31,96      | 105,27          |

| 2,24 m                             | 1        | 1003,21        | 2006,42          | 33,7  | 30,54      | 114,77          |

| 1,25 m                             | 10       | 100,32         | 200,64           | 18,8  | 25,49      | 164,23          |

| 490 $\mu$                          | 10<br>0  | 10,03          | 20,06            | 7,35  | 17,33      | 339,30          |

| <i>Projetos para o MOSFET PMOS</i> |          |                |                  |       |            |                 |

| $g_m$ (S)                          | $i_f$    | $W/L$          | $W(\mu\text{m})$ | $A_v$ | $A_v$ (dB) | $V_{Dsat}$ (mV) |

| 2,50 m                             | 0,1<br>9 | 32020,4<br>0,5 | 64040,9<br>8     | 37,51 | 31,49      | 105,27          |

| 2,12 m                             | 1        | 3202,05        | 6404,09<br>8     | 31,9  | 30,06      | 114,77          |

| 1,19 m                             | 10       | 320,20         | 640,41           | 17,8  | 25,02      | 164,23          |

| 464 $\mu$                          | 10<br>0  | 32,02          | 64,04            | 6,96  | 16,85      | 339,30          |

As especificações arbitrárias foram de um ganho de tensão  $A_v = 7$ , tensão de alimentação  $V_{DD} = 3$  V, tensão de polarização na saída de  $V_o = V_{DD}/2$  e a corrente de dreno  $I_D = 100 \mu\text{A}$ . Com essas especificações aplicadas na equação (9), resultou em um valor de  $R_D = 15 \text{ k}\Omega$ . A aplicação do valor de  $R_D$  e do ganho  $A_v$  na equação (8), juntamente com os parâmetros tecnológicos apresentados na Seção 2.1 e os valores apresentados na Tabela 2, resulta em um  $g_m = 479,667 \mu\text{S}$ .

Para o projeto do transistor, o valor de corrente de dreno e de transcondutância foram aplicados na equação (4) para definição dos valores da razão de aspecto  $W/L$ . O valor do comprimento do canal foi arbitrado em  $L = 2 \mu\text{m}$  para que se possa garantir a precisão dos modelos de canal longo. Uma planilha de cálculo foi desenvolvida para fazer a automatização desses cálculos e os resultados podem ser verificados na Tabela 3.

Os valores de nível de inversão foram alterados para verificar demais valores de ganho e entender se o macro-modelo teria confiabilidade em qualquer região de operação do transistor. Para o ganho especificado, o transistor resultou em uma operação em nível de inversão forte  $i_f = 100$ ; isso resulta em um transistor de área menor, com relação a outros níveis de inversão. No entanto, uma desvantagem é a tensão de saturação que aumenta com o nível de inversão, reduzindo assim a faixa dinâmica do amplificador em questão. A utilização de um nível de inversão menor resulta em maiores  $g_m$  e, portanto, maiores ganhos. Assim, pode-se tanto alterar a corrente de dreno quanto a resistência de carga para se ajustar o ganho.

Os valores não foram ajustados simplesmente pelo fato de não interessar chegar a um ganho específico, mas sim verificar a confiabilidade da simulação. Então, os resultados de simulação servirão para comparar os valores de ganho apresentados na Tabela 3.

### 3.3 Projeto do amplificador de transcondutância

Iniciou-se o projeto dos transistores do OTA, apresentado na Figura 2, pelos transistores do par diferencial de entrada. Utilizando  $g_{mg} = 1,88 \text{ mS}$  pode-se calcular, com a equação (4), a razão de aspecto para uma corrente de dreno de  $80 \mu\text{A}$ . Já para o cálculo das razões de aspecto dos transistores do espelho *cascode* parte-se do valor de corrente de  $240 \mu\text{A}$  e define-se a tensão  $V_{DS}$  de saturação máxima que se deseja para se definir o nível de inversão com a equação (5). No caso dos transistores do espelho, obteve-se um nível de inversão próximo de 10 para um  $V_{SD(sat)}$  de aproximadamente  $160 \text{ mV}$  para cada um dos transistores do espelho. No caso dos transistores T12 e T13 é preciso considerar a corrente do par diferencial de entrada somada.

Para o circuito de polarização, apresentado na Figura 1(A), procedeu-se o projeto da seguinte forma. O nó chamado de *Vbias\_1* se refere ao espelho de corrente de cauda do amplificador diferencial de entrada. Então, para a definição da razão de aspecto do transistor T1 basta aplicar a razão entre as correntes de dreno dos transistores T14 e T1; neste caso, como a corrente de dreno do transistor T14 deveria ser aproximadamente  $160 \mu\text{A}$  e a corrente de dreno do transistor T1 foi definida como  $1 \mu\text{A}$ , obtém-se uma razão de 160 que pode ser aplicada diretamente à razão de aspecto entre os transistores. O transistor T14 também foi projetado para estar em inversão fraca, ou seja, próximo do valor 1, para que a sua tensão de saturação não ultrapasse  $150 \text{ mV}$ . O transistor T2 e T4 replicam corrente de  $3 \mu\text{A}$  e  $1 \mu\text{A}$ , respectivamente, para polarizar os transistores T3 e T5. Para o caso do transistor T5 basta fazer o mesmo procedimento utilizado para o transistor T14.

O transistor T3 não poderá ser polarizado da mesma forma que os outros porque ele polariza os transistores T11 e T10 do espelho *cascode* e estes, por estarem empilhados, apresentam um potencial  $V_S$  diferente de zero. Isso altera o nível de inversão, segundo as equações (6) e (7), e por consequência a tensão  $V_{GS}$  necessária para polarizar o transistor em um determinado nível de inversão em comparação com a situação de  $V_S = 0 \text{ V}$ . Então, um potencial  $V_S$  de três vezes o  $V_{DS(sat)}$  dos transistores T12 e T13 foi utilizado como referência para ser o potencial  $V_S$  de T10 e T11, para que um nível de inversão fosse definido para T3 de forma que a tensão de *pinch off* ( $V_p$ ) fosse igual à tensão de *pinch off* para os transistores T10 e T11. Com os critérios aqui apresentados, o projeto dos transistores pode ser verificado na Tabela 4.

O circuito apresentado na Figura 1(A) e na Figura 1(B) foi compilado em um macromodelo *SPICE* chamado de OTA001V2 para que os diagramas esquemáticos das simulações de teste apresentassem aspecto mais simplificado. Os resultados dos testes de desempenho do amplificador de transcondutância são apresentados na Seção 4, subseção 4.2.

## 4 RESULTADOS E DISCUSSÕES

Os resultados da extração dos parâmetros via simulação *SPICE* e sua respectiva comparação com os resultados da extração de parâmetros via mapeamento das informações tecnológicas fornecidas para o modelo BSIM apresentaram um erro de máximo de aproximadamente 17% com relação a corrente específica do PMOS e de 17% com relação a tensão de limiar do NMOS. Neste momento estes valores serão considerados aceitáveis para a função

Tabela 4: Resumo do projeto dos transistores.

| Transistor      | W/L    | L ( $\mu\text{m}$ ) | W ( $\mu\text{m}$ ) |

|-----------------|--------|---------------------|---------------------|

| T1 e T4         | 2,65   | 2                   | 5,3                 |

| T2              | 7,95   | 2                   | 15,9                |

| T3              | 0,0795 | 20                  | 1,59                |

| T5              | 1      | 2                   | 2                   |

| T6, T7, T8 e T9 | 632    | 1                   | 632                 |

| T10 e T11       | 242    | 1                   | 242                 |

| T12 e T13       | 323    | 1                   | 323                 |

| T14             | 422    | 1                   | 422                 |

deste teste que é de confirmar que o macromodelo desenvolvido simula de forma aceitável o transistor integrado. A partir daqui se apresentará os resultados dos projetos realizados.

#### 4.1 Amplificador fonte comum

Os diagramas esquemáticos utilizados para a simulação dos amplificadores fonte comum (FC) podem ser verificados na Figura 4 (A) e na Figura 4 (B). A polarização do transistor foi feita via espelho de corrente para dar maior precisão e por simplicidade. As mudanças de ganho serão realizadas apenas alterando a largura dos transistores o restante dos parâmetros de simulação se manteve inalterado.

Figura 4: (A) amplificador FC NMOS e (B) amplificador FC PMOS.

Simulações de ponto de operação para cada largura de canal apresentada na Tabela 3 foram realizadas para verificar a especificação de tensão de polarização na saída. Após esta, foram realizadas, para as mesmas situações, uma simulação de resposta em frequência para a verificação do ganho em dB. E, por fim, uma simulação transitória na situação de  $W = 20 \mu\text{m}$  foi realizada para verificar o funcionamento em modo transitório.

Tabela 5: Resultados de simulação e respectivos erros com relação às especificações de projeto.

| Resultados para o amplificador NMOS |               |          |                         |          |            |          |

|-------------------------------------|---------------|----------|-------------------------|----------|------------|----------|

| $W$ ( $\mu\text{m}$ )               | $V_{oCC}$ (V) | Erro (%) | $I_D$ ( $\mu\text{A}$ ) | Erro (%) | $A_v$ (dB) | Erro (%) |

| 20064                               | 1,29          | 14       | 114                     | 11,4     | 30,68      | 4,2      |

| 2006                                | 1,32          | 12       | 111,78                  | 11,78    | 30,07      | 1,5      |

| 200                                 | 1,38          | 8        | 107,71                  | 7,7      | 27,55      | 8,08     |

| 20                                  | 1,46          | 2,667    | 102,6                   | 2,6      | 19,47      | 12,35    |

| Resultados para o amplificador PMOS |               |          |                         |          |            |          |

| $W$ ( $\mu\text{m}$ )               | $V_{oCC}$ (V) | Erro (%) | $I_D$ ( $\mu\text{A}$ ) | Erro (%) | $A_v$ (dB) | Erro (%) |

| 64040                               | 1,61          | 7,33     | 107,29                  | 7,29     | 30,99      | 3        |

| 6404                                | 1,6           | 6,67     | 106,34                  | 6,34     | 30,24      | 0,6      |

| 640                                 | 1,57          | 4,67     | 104,7                   | 4,7      | 27,13      | 6,43     |

| 64                                  | 1,53          | 2        | 102,22                  | 2,22     | 17,96      | 3,6      |

Os resultados de polarização CC e de ganho estão resumidos na Tabela 5, onde verifica-se a tensão de polarização CC no dreno dos transistores ( $V_{oCC}$ ), a corrente de dreno CC ( $I_D$ ) e o ganho em dB proveniente de simulação de resposta em frequência. Os erros apresentados são relativos aos valores especificados no projeto de  $V_{oCC} = 1,5$  V,  $I_D = 100 \mu\text{A}$  e o ganho calculado e apresentado na Tabela 3.

Pode-se verificar que esses valores são consistentes com as especificações, apresentando erros máximos da ordem de 12%. Isso mostra que os modelos de simulação mantêm uma consistência com relação ao modelo utilizado para o cálculo do projeto e mostra confiabilidade com relação aos macromodelos de simulação.

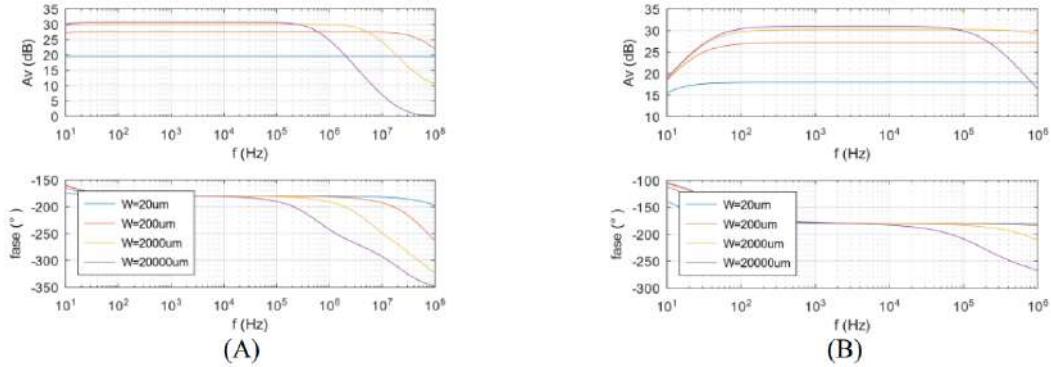

Figura 5: Resposta em frequência para o macromodelo (A) NMOS e (B) PMOS.

Pode-se verificar a resposta em frequência completa para o macromodelo do transistor NMOS na Figura 5(A). Nela verifica-se, além dos valores dos ganhos em banda plana, o giro de fase de  $180^\circ$  de amplificadores inversores. No caso do ganho e da fase, pode-se observar a mudança das capacitâncias intrínsecas ao transistor conforme há a mudança no nível de inversão e dimensões dos transistores. Essas mudanças podem ser observadas nas mudanças das frequências de corte para cada caso. Esses resultados demonstram uma coerência que, neste momento, ainda manteremos como intuitiva, de que quanto maior o transistor e menor o nível de inversão, maiores são as capacitâncias intrínsecas dos transistores. A Figura 5(B) apresenta os mesmos resultados para os projetos usando o macromodelo do transistor PMOS. As conclusões são semelhantes às anteriores.

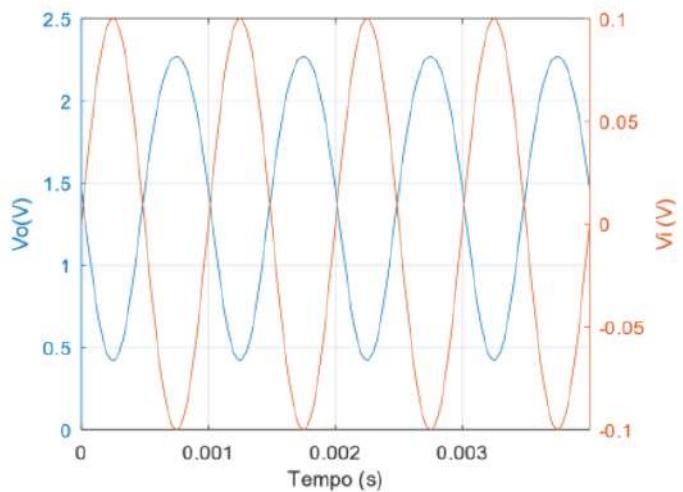

Para finalizar esta análise, a Figura 6 apresenta uma simulação transitória para demonstrar a validade dos macromodelos para simulações transitórias, apenas para fins de ilustração. Na figura citada pode-se verificar o ganho e a inversão de fase característica do amplificador fonte comum.

#### 4.2 Operational transconductance amplifier

Para a verificação dos pontos de operação e das correntes projetadas realizou-se uma simulação de ponto de operação com o OTA em configuração de seguidor de tensão. A corrente de dreno de T14 é de  $153,08\mu\text{A}$ , o que resulta em correntes em cada um dos transistores do par diferencial de entrada de  $76,54\mu\text{A}$ . Estes valores apresentam valor de aproximadamente  $3,5\mu\text{A}$  menor do que os  $80\mu\text{A}$  originalmente projetados. Entende-se que esta discrepância não afetará o  $GBW$  de forma significativa.

As correntes no espelho *cascode* foram de  $183,9\mu\text{A}$ . Já estas correntes apresentaram discrepância de aproximadamente  $58\mu\text{A}$  em relação aos  $240\mu\text{A}$  pretendidos. Isso provavelmente causará impactos tanto no ganho de malha aberta quanto no *SR* do OTA. Um pequeno ajuste no ganho do espelho, reduzindo o *W* do transistor T5 para  $1,7\mu\text{m}$ , já corrigiria esta situação. No entanto, é sempre desaconselhável fazer ajustes de simulação sem uma compreensão da razão desta discrepância. Esse assunto será investigado posteriormente com o aprofundamento do estudo de circuitos integrados CMOS, que continua a ser explorado pelo autor.

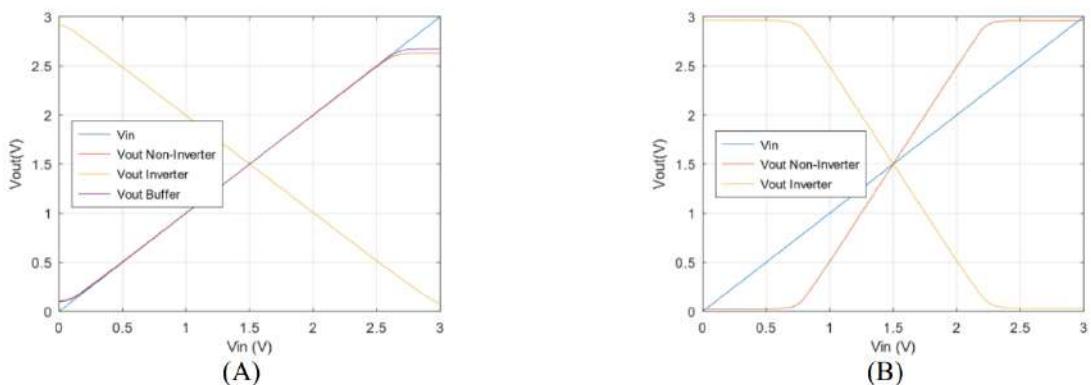

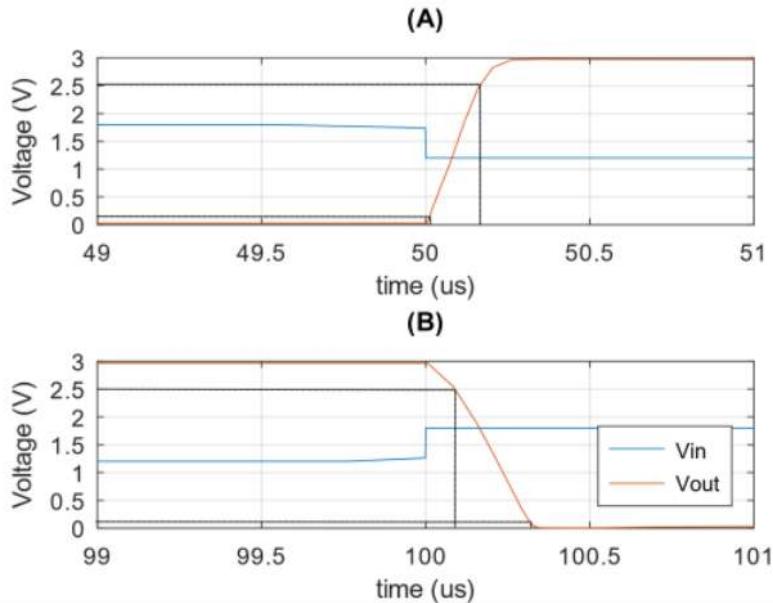

**Figura 7:** Resultados para o teste de faixa dinâmica na saída (A) para ganho 1 e (B) para ganho 2.

Os testes tiveram continuidade mesmo com as correntes do espelho não apresentarem o valor projetado. Uma das figuras de mérito para amplificadores de transcondutância e amplificadores operacionais é a faixa dinâmica na saída do amplificador e a faixa de tensão de modo comum na entrada. Para esse teste foram feitas três configurações, que são: o amplificador seguidor de tensão (*Buffer*), o amplificador não inversor com ganho unitário e o

amplificador inversor com ganho unitário. O OTA foi alimentado com tensão de alimentação simples de 3 V ( $V_1$ ) e foi realizado um *sweep* na tensão CC de entrada ( $V_2$ ) entre 0 V e 3 V.

Os resultados podem ser verificados na Figura 7(A), onde a faixa de tensão de saída mais restrita para o amplificador é de aproximadamente 0,3 V a 2,6 V quando alimentado com alimentação simples de 3 V. A faixa permitida de tensão de entrada é de 300 mV até 2,6 V. Esses resultados mostram que, se forem respeitados estes limites, o amplificador funcionará de forma linear.

O resultado apresentado na Figura 7(A) com ganho 1 representa melhor as limitações na tensão de modo comum de entrada. Para ter uma ideia da faixa dinâmica na saída, ainda se realiza um segundo teste com um ganho diferente de um. Neste caso, foram montados um amplificador não inversor e um inversor de ganho 2 para ambos, e nas entradas foi aplicado o mesmo *sweep* do teste anterior. Este resultado pode ser verificado na Figura 7(B), com a tensão de saída saturando a aproximadamente 24 mV em relação à alimentação negativa e 40 mV com relação à alimentação positiva, tanto para o amplificador inversor quanto para o amplificador não inversor. Esta estrutura poderia ser considerada um amplificador *rail-to-rail* na saída.

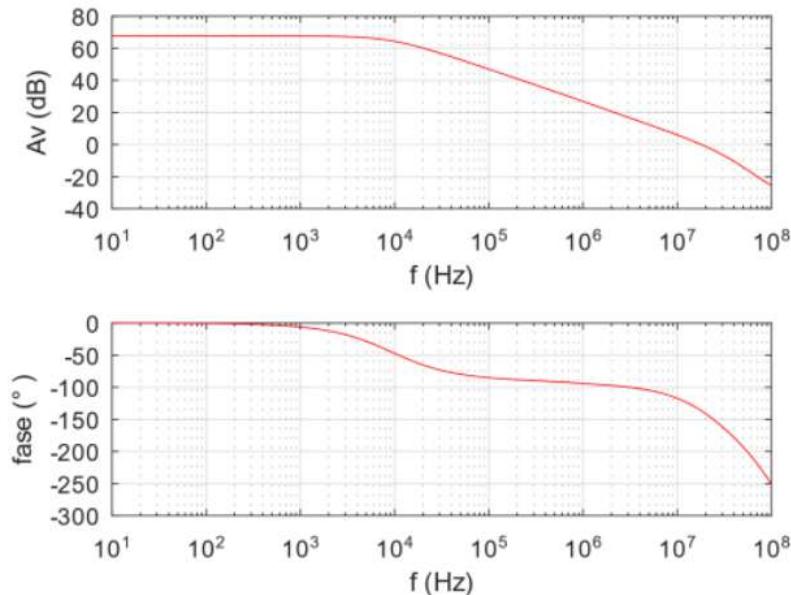

Figura 8: Resposta em frequência do OTA.

Seguindo com as simulações de desempenho do OTA projetado, a Figura 9 apresenta o resultado de simulação de resposta em frequência por meio de diagrama de Bode. Para este teste foi montado um amplificador não inversor com ganho 10001 (Sedra, 2014) e, com um gerador de sinal na entrada, fez-se uma simulação de curva característica AC. Essa análise permite verificar o ganho de malha aberta, o  $GBW$  e as margens de ganho e fase. Pode-se verificar que o ganho de malha aberta é de 67,67 dB, o  $GBW$  é de 17,95 MHz, a margem de ganho é de 10,74 dB aproximadamente e a margem de fase é 44,17°.

Do ponto de vista de especificações, o projeto acabou não alcançando as especificações de desempenho de resposta em frequência. Isso pode ser uma consequência da discrepância entre a corrente especificada e a corrente calculada pelo simulador no espelho *cascode*. Essa discrepância pode ser explicada por questões de efeitos de canal curto que diminuem as transcondutâncias de dreno dos transistores e, assim, descasando os espelhos de polarização. Faz-se necessária uma investigação mais detalhada desta questão. Apesar de não alcançar as especificações originais da maneira como foi executado, ainda é um amplificador com características apreciáveis para diversas aplicações.

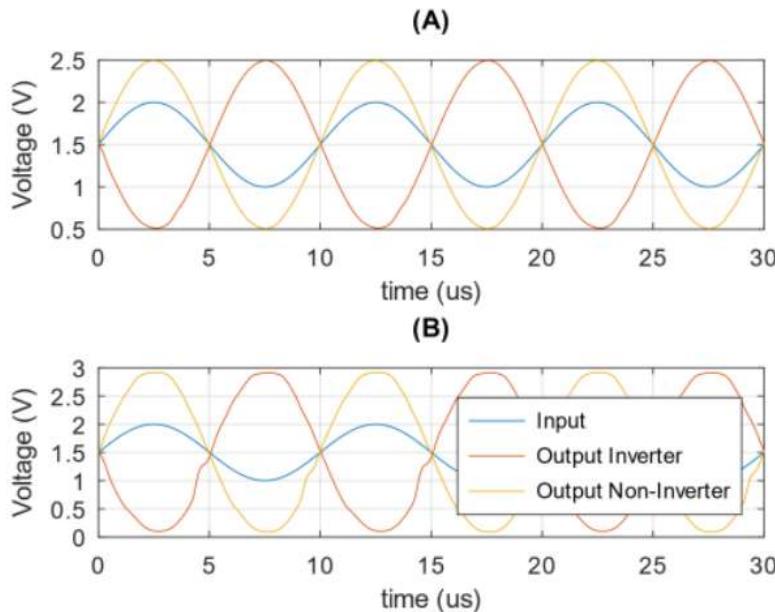

Continuando a verificação de desempenho, fez-se também a análise de velocidade limite do amplificador na saída através da medida do *slew rate*. Para este teste montou-se um amplificador inversor com ganho 1000 utilizando o macromodelo *SPICE* do OTA projetado. A Figura 10(A) mostra o comportamento de um amplificador de ganho 1000 na transição entre níveis de um sinal retangular na entrada, representando para a saída uma transição de

subida que resulta em uma taxa de aumento na tensão de aproximadamente  $15 \text{ V}/\mu\text{s}$ . Já a Figura 10(B) apresenta a mesma situação, mas para uma transição de descida do sinal de saída de aproximadamente  $10,4 \text{ V}/\mu\text{s}$ . Neste caso, apenas o *SR* de subida se apresentou condizente com a especificação dada. Mas, apesar de ser mais lento para a descida, o amplificador apresenta um desempenho aceitável para uma grande variedade de aplicações.

**Figura 9:** (A) *Slew rate* de subida e (B) *slew rate* de descida.

O último teste realizado foi o de resposta transiente com excitação senoidal. Foram testados dois ganhos diferentes em um amplificador inversor e em um amplificador não inversor para verificar a funcionalidade linear e a distorção nos limites de tensão de alimentação. Neste último pode-se avaliar novamente a faixa dinâmica da tensão de saída. O sinal de excitação foi um sinal senoidal de 0,5 V de amplitude, 1,5 V de valor médio e frequência de 100 kHz.

Pode-se observar o correto funcionamento tanto do amplificador inversor quanto do amplificador não inversor em ambos os casos apresentados na Figura 11(A). Com ganho 2, é possível verificar a exatidão do ganho e a linearidade da operação. Já na Figura 11(B) pode-se verificar, com ganho de 3, a saturação com a tensão de saída sendo limitada ao seu limite de faixa dinâmica. Na Figura 11(B) pode-se verificar os limites de faixa dinâmica de saída que foram verificados anteriormente na Figura 8.

O circuito proposto não alcançou todas as especificações primeiramente determinadas, mas apresentou um desempenho compatível com diversas aplicações de amplificadores de transcondutância, qualificando sua utilização. Para completar o objetivo deste trabalho, propõe-se a utilização deste amplificador de transcondutância em uma fonte de corrente controlada por tensão, com aplicação como fonte excitadora de um dispositivo de espectroscopia de bioimpedância elétrica.

## 5 PROPOSTA DE FONTE DE CORRENTE UTILIZANDO O OTA

A primeira proposta de fonte de corrente controlada por tensão que foi utilizada como teste foi a encontrada em (Silverio; Silverio, 2012). O autor propõe uma fonte de corrente controlada por tensão baseada em um OTA com aplicação em espectroscopia de bioimpedância elétrica. Pelo fato de um dos objetivos deste trabalho ter sido o de projetar um OTA, então a aplicação dele em espectroscopia de bioimpedância elétrica foi uma escolha natural. No artigo citado, o autor projeta um OTA em tecnologia CMOS  $0,35 \mu\text{m}$  para aplicá-lo a um conversor tensão-corrente inversor integrado. Para aumentar a impedância de entrada do circuito inversor, ele utiliza um tipo de circuito *buffer* chamado de *current conveyor*, também projetado na mesma tecnologia, formando assim uma fonte de corrente controlada por tensão integrada.

**Figura 10:** Simulação transiente do amplificador inversor e não inversor.

Baseado nesta ideia, pretende-se fazer uma avaliação do uso do OTA projetado para este trabalho em uma fonte de corrente controlada por tensão não inversora. Isso tornaria o circuito mais simples, pois a impedância de entrada alta é conseguida pela entrada não inversora do OTA.

## 6 CONSIDERAÇÕES FINAIS

O estudo, revisão e reaprendizagem de projeto de circuitos integrados analógicos foi um passo que levou mais tempo que o esperado, mas foi necessário fazê-lo, de forma cuidadosa, para que o autor pudesse readquirir habilidades e conhecimentos básicos fundamentais para a qualidade de projetos posteriores do circuito integrado pretendido pelo grupo. Ainda será necessário mais estudo, que será realizado no decorrer das próximas etapas. Outro passo que teve que ser feito com mais cuidado foi o do desenvolvimento e validação do macromodelo do transistor para simulação SPICE. Isso porque era necessário adquirir confiança nos resultados que se apresentavam a cada passo dado, inclusive realizando simulações adicionais com outros simuladores SPICE utilizando o mesmo macromodelo.

Os resultados apresentados demonstram que o modelo analítico utilizado para o projeto se mostrou confiável e eficiente para a definição das dimensões físicas dos transistores. O macromodelo SPICE desenvolvido juntamente com o simulador escolhido demonstraram bom desempenho e a capacidade de simular com confiabilidade os projetos realizados. Pode-se verificar isso em todos os resultados de projetos realizados. Ainda são necessários ajustes e estudos com relação à topologia e projeto de OTAs para reduzir a discrepância encontrada nos espelhos de corrente *cascode*. Mas o simulador será de grande importância nesta exploração e nas demais que virão com o objetivo de trazer o melhor desempenho para o sistema do glicômetro.

Assim sendo, para trabalhos futuros, pretende-se revisar a literatura sobre fontes de corrente controladas por tensão CMOS para aplicação em espectroscopia de bioimpedância elétrica. Além disso, serão pesquisadas e feitas explorações via simulação do projeto CMOS para os demais circuitos necessários para a construção do sistema do glicômetro não invasivo como, por exemplo, amplificadores de instrumentação, amplificadores de transimpedância, referências de tensão e corrente para a polarização dos circuitos, dentre outros que poderão vir a ser necessários. Isso será possível a partir da confiança adquirida neste trabalho, tanto do modelo analítico quanto no macromodelo desenvolvido e no simulador utilizado.

## 7 AGRADECIMENTOS

Este trabalho contou com financiamento conjunto da Universidade do Estado de Santa Catarina (UDESC), Fundação de Amparo à Pesquisa e Inovação do Estado de Santa Catarina (FAPESC) e Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq).

**REFERÊNCIAS**

- ADORNES, C. M. *et al.* Bridging the gap between design and simulation of low-voltage cmos circuits. **Journal of Low Power Electronics and Applications**, v. 12, n. 2, p. 34, jun 2022.

- ADVANCED compact MOSFET. Disponível em: [https://lci.ufsc.br/acm/handy\\_design.html](https://lci.ufsc.br/acm/handy_design.html).

- COITINHO, R. M.; SPILLER, L. H.; SCHNEIDER, M. Metodologia simplificada de extração de parâmetros para o modelo acm do transistor mos. In: **VII Workshop de Iberchip**. Montevidéu, Uruguay.: IWS 2001, 2000.

- CORBACHO, I. *et al.* Wide-bandwidth electronically programmable cmos instrumentation amplifier for bioimpedance spectroscopy. **IEEE Access**, v. 10, p. 95604–95612, 2022.

- MACHADO, M. B. *et al.* Mosfet threshold voltage: definition, extraction, and applications. In: **Proceedings of Nanotech**. Federal University of Santa Catarina – UFSC: Department of Electrical Engineering, 2011. v. 2, p. 710–713.

- MIAO, F. *et al.* Wearable sensing, big data technology for cardiovascular healthcare: current status and future prospective. **Chinese Medical Journal**, v. 136, n. 9, p. 1015–1025, 2023.

- MIZUNO, A.; CHANGOLKAR, S.; PATEL, M. S. Wearable devices to monitor and reduce the risk of cardiovascular disease: evidence and opportunities. **Annual Review of Medicine**, v. 72, p. 459–471, 2021.

- SANTOS, P. M. d. **Eletrônica geral**. Minas Gerais: Campus Nova Gameleira, 2022. Disponível em: [https://bookdown.org/patrickcefet/eletronica\\_geral/](https://bookdown.org/patrickcefet/eletronica_geral/).

- SCHNEIDER, M. C.; GALUP-MONTORO, C. **CMOS analog design using all-region MOSFET modeling**. United Kingdom: Cambridge University Press, 2010.

- SEDRA, A. **Microelectronic circuits**. 7. ed. New York: Oxford University Press, 2014.

- SIEBEL, O. F.; GALUP-MONTORO, C. **Um modelo eficiente do transistor MOS para o projeto de circuitos VLSI**. Tese (Doutorado) — Centro Tecnológico. Programa de Pós-Graduação em Engenharia Elétrica, Universidade Federal de Santa Catarina, 2007.

- SILVERIO, E. A. A.; SILVERIO, E. A. A. A high output impedance current source for wideband bioimpedance spectroscopy using 0.35 µm tsmc cmos technology. **International Journal of Engineering**, v. 1, n. 2, p. 2305–8269, 2012.

- VALENTE, V.; DEMOSTHENOUS, A. Wideband fully-programmable dual-mode cmos analogue front-end for electrical impedance spectroscopy. **Sensors**, v. 16, n. 8, p. 1159, ago. 2016.

- VIJAYAN, V. *et al.* Review of wearable devices and data collection considerations for connected health. **Sensors**, v. 21, n. 16, p. 5589, 2021.

- VOGTT, H.; ATKINSON, G.; NENZI, P.; WARNING, D. **Ngspice user's manual version 40 plus (ngspice release version)**. University of California, 2023. Disponível em: <https://ngspice.sourceforge.io/docs/ngspice-40-manual.pdf>.